# Precision Adjustable Current Limited Power Distribution Switches

#### 1 FEATURES

- Up to 3A Maximum Load Current

- Typical 100µA Low Quiescent Current

- Typical 0.1µA Shutdown Current

- No Reversed Leakage Current When Power Off

- Meets USB Current Limiting Requirements

- Adjustable Current Limit: 500mA to 3A

- Fast Over-Current Response: 2μs

- 50mΩ High-side MOSFET

- Reverse Input-Output Voltage Protection

- Under Voltage Lockout

- Thermal Shutdown Protection

- Operating Range: 2.5V to 5.5V

- Built-In Soft-Start Function

- Available in the Green DFN3×3-8L Package

#### **2 APPLICATIONS**

- USB Host and Self-Powered Bubs

- USB Bus-Powered Hubs

- USB Power Management

- General Purpose Power Switch (High Side)

- Hot Plug-in Power Supplies

- Battery-Charger Circuits

#### 3 DESCRIPTION

The RS2599 is an integrated power switch for self-powered and bus-powered Universal Serial Bus (USB) applications.

The RS2599 is a cost-effective, low voltage, single P-channel MOSFET load switch with  $50m\Omega$  R<sub>DS(ON)</sub>, which is free of parasitic body diode to eliminate any reversed current flow across the switch when it is powered off. When the output voltage is higher than input voltage, the power switch is turned off by internal output reverse-voltage protector.

Several Protection features include current limiting and thermal shutdown to prevent catastrophic switch failure caused by increasing power dissipation when continuous heavy loads or short circuit occurs.

FLAG is an open-drain output report over-current or over-temperature event and has typical 13ms deglitch timeout period. In addition, FLAG also reports output reverse-voltage condition with typical 5ms deglitch timeout period.

RS2599 is available in the Green DFN3x3-8L package. It is rated over the -40°C to +85°C temperature range.

#### **Device Information (1)**

| PART NUMBER | PACKAGE   | BODY SIZE (NOM) |

|-------------|-----------|-----------------|

| RS2599      | DFN3×3-8L | 3.00mm×3.00mm   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

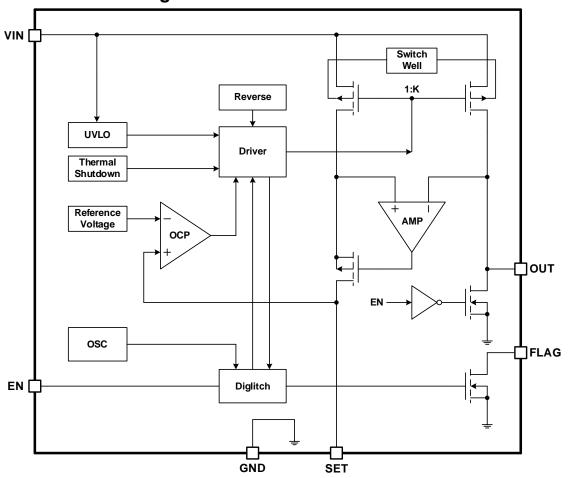

# 4 Functional Block Diagram

### **Table of Contents**

| 1 FEATURES                                        | 1  |

|---------------------------------------------------|----|

| 2 APPLICATIONS                                    | 1  |

| 3 DESCRIPTION                                     | 1  |

| 4 Functional Block Diagram                        | 2  |

| 5 Revision History                                | 4  |

| 6 PACKAGE/ORDERING INFORMATION                    | 5  |

| 7 PIN CONFIGURATIONS                              | 6  |

| 8 Specifications                                  | 7  |

| 8.1 Absolute Maximum Ratings (1)                  | 7  |

| 8.2 ESD Ratings                                   | 7  |

| 8.3 Recommended Operating Rating                  | 7  |

| 8.4 Thermal Information                           | 8  |

| 8.5 ELECTRICAL CHARACTERISTICS                    | 9  |

| 8.6 PARAMETER MEASUREMENT INFORMATION             | 10 |

| 8.7 TYPICAL PERFORMANCE CHARACTERISTICS           | 11 |

| 9 DETAILED DESCRIPTION                            | 13 |

| 9.1 Input and Output                              | 13 |

| 9.2 Thermal Shutdown                              | 13 |

| 9.3 Soft-Start                                    | 13 |

| 9.4 Under-Voltage Lockout (UVLO)                  | 13 |

| 9.5 Current Limiting and Short-Circuit Protection | 13 |

| 9.6 Reverse-Voltage Protection                    | 13 |

| 9.7 Fault Flag (FLAG)                             | 13 |

| 9.8 Power Dissipation                             | 13 |

| 9.9 Supply Filter Capacitor                       | 14 |

| 9.10 Output Filter Capacitor                      | 14 |

| 9.11 PCB Layout Guide                             | 14 |

| 10 PACKAGE OUTLINE DIMENSIONS                     | 15 |

| 11 TARE AND REEL INCORMATION                      | 16 |

**5 Revision History**Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION                                                                                                                                                         | Change Date                               | Change Item               |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|--|--|--|

| A.0                                                                                                                                                             | 2021/11/26                                | Initial version completed |  |  |  |

| A.1                                                                                                                                                             | A.1 2022/05/05 Official version completed |                           |  |  |  |

| A.2  2022/08/29  1. Update I <sub>LIMIT</sub> , I <sub>SHORT</sub> PARAMETER on Page 8@RevA.1 2. Update Current Limiting and Short-Circuit Protection on Page 1 |                                           |                           |  |  |  |

### 6 PACKAGE/ORDERING INFORMATION (1)

| PRODUCT | ORDERING<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE<br>LEAD | PACKAGE<br>MARKING (2) | PACKAGE OPTION     |  |

|---------|--------------------|----------------------|-----------------|------------------------|--------------------|--|

| RS2599  | RS2599YTDC8        | -40°C ~+85°C         | DFN3×3-8L       | RS2599                 | Tape and Reel,5000 |  |

#### NOTE:

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) There may be additional marking, which relates to the lot trace code information(data code and vendor code), the logo or the environmental category on the device.

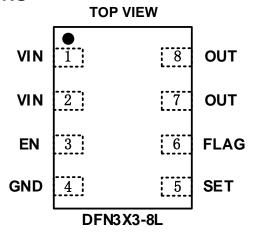

## **7 PIN CONFIGURATIONS**

#### **PIN DESCRIPTION**

| PIN       | NAME | DESCRIPTION                                                                                                                                                               |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFN3×3-8L |      | DESCRIPTION                                                                                                                                                               |

| 1         | VIN  | Power Supply Input. The P-Channel Source of Switch, Which also supplies IC's internal                                                                                     |

| 2         | VIIN | circuitry. Connect to Positive Supply.                                                                                                                                    |

| 3         | EN   | Enable Input. Logic Level Enable Input, Active high available.                                                                                                            |

| 4         | GND  | Ground.                                                                                                                                                                   |

| 5         | SET  | Current limit set pin. Connect a resistor between this pin and ground to program the desired current limit set point.                                                     |

| 6         | FLAG | Fault Flag. Active low, open-drain output. Indicates over-current or thermal shutdown conditions. Over-current condition must last longer than td in order to assert FLAG |

| 7         | OUT  | Switch Output. The P-Channel Drain of Switch, Which Typically Connects to Load.                                                                                           |

| 8         | 001  | Switch Output. The r-Chainlet Drain of Switch, Which Typically Conflects to Load.                                                                                         |

#### 8 Specifications

#### 8.1 Absolute Maximum Ratings (1)

over operating free-air temperature range (unless otherwise noted) (1)

|                   |                                     | MIN  | MAX | UNIT |

|-------------------|-------------------------------------|------|-----|------|

| V <sub>IN</sub>   | Supply voltage range                | -0.3 | 6.0 | V    |

| V <sub>OUT</sub>  | Output voltage range                | -0.3 | 6.0 | V    |

| V <sub>EN</sub>   | EN Input Voltage                    | -0.3 | 6.0 | V    |

| V <sub>FLAG</sub> | FLAG Output Voltage                 | -0.3 | 6.0 | V    |

| Vset              | SET Output Voltage                  | -0.3 | 6.0 | V    |

| TJ                | Junction temperature (2)            | -40  | 150 | °C   |

| T <sub>stg</sub>  | Storage temperature                 | -65  | 150 | °C   |

| T∟                | Lead Temperature (Soldering,10secs) |      | 260 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 8.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                    | -                        |                                                                                             | VALUE | UNIT |  |

|--------------------|--------------------------|---------------------------------------------------------------------------------------------|-------|------|--|

| V(50D)             | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                           | ±6000 | V    |  |

| V <sub>(ESD)</sub> | Electrostatic discriarge | ctrostatic discharge  Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> |       |      |  |

<sup>(1)</sup> JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

#### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

8.3 Recommended Operating Rating

|                   |                       | MIN | MAX | UNIT |

|-------------------|-----------------------|-----|-----|------|

| V <sub>IN</sub>   | Supply voltage range  | 2.5 | 5.5 | V    |

| Vout              | Output voltage range  | 0   | 5.5 | V    |

| V <sub>EN</sub>   | EN Input Voltage      | 0   | 5.5 | V    |

| V <sub>FLAG</sub> | FLAG Output Voltage   | 0   | 5.5 | V    |

| Vset              | SET Output Voltage    | 0   | 5.5 | V    |

| T <sub>A</sub>    | Operating Temperature | -40 | 85  | °C   |

<sup>(2)</sup> The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

### 8.4 Thermal Information

|                       |                                              | RS2599    |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC (1)                           | 8PINS     | UNIT |

|                       |                                              | DFN3×3-8L |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 66.9      | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case(top) thermal resistance     | 54.5      | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 40.4      | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 1.9       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 40.4      | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case(bottom) thermal resistance  | 10.8      | °C/W |

<sup>(1)</sup> Thermal resistance varies with operating conditions.

#### 8.5 ELECTRICAL CHARACTERISTICS

( $V_{IN}=5.0V$ ,  $T_A=+25$ °C, unless otherwise noted.) (1)

| PARAMETER                                  | SYMBOL                 | TEST CONDITIONS                                                                          | MIN (2) | TYP (3) | MAX (2) | UNIT |

|--------------------------------------------|------------------------|------------------------------------------------------------------------------------------|---------|---------|---------|------|

| Power Input Voltage Range                  | V <sub>IN</sub>        |                                                                                          | 2.5     |         | 5.5     | V    |

| Power Supply Current                       | ΙQ                     | Switch on, Vout=Open                                                                     |         | 100     | 200     | μΑ   |

| Shutdown Supply Current                    | I <sub>SD</sub>        | Switch off, Vout=Open                                                                    |         | 0.1     | 1.0     | μΑ   |

| Under-Voltage Lockout Threshold            | V <sub>UVLO</sub>      | C <sub>IN</sub> =10µF                                                                    |         | 1.9     | 2.4     | V    |

| Under-Voltage Lockout Threshold Hysteresis | Vuvlo_hy               | C <sub>IN</sub> =10µF                                                                    |         | 0.1     | 0.2     | V    |

| High-side MOSFET On Resistance             | R <sub>DS(ON)</sub>    | І <sub>ОUТ</sub> =500mA                                                                  |         | 50      | 60      | mΩ   |

| Franka Innut Threshold                     | V <sub>IH</sub>        | V <sub>IN</sub> =2.5V to 5.5V, C <sub>IN</sub> =10μF                                     | 1.6     |         |         | V    |

| Enable Input Threshold                     | VIL                    | V <sub>IN</sub> =2.5V to 5.5V, C <sub>IN</sub> =10µF                                     |         |         | 0.4     | V    |

| Enable Input Current                       | I <sub>EN</sub>        | V <sub>EN</sub> = 5V                                                                     |         | 10      | 20      | μΑ   |

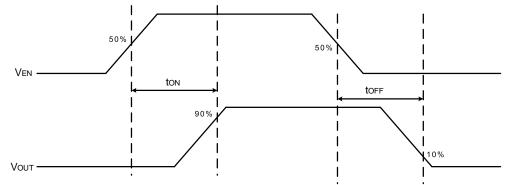

| Output Turn-On Delay Time                  | ton                    | C <sub>IN</sub> =10μF, R <sub>L</sub> =10Ω, C <sub>L</sub> =1μF                          |         | 2.0     | 3.0     | ms   |

| Output Turn-Off Delay Time                 | toff                   | C <sub>IN</sub> =10μF, R <sub>L</sub> =10Ω, C <sub>L</sub> =1μF                          |         | 20      | 30      | μs   |

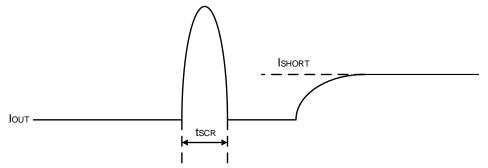

| Response Time to Short Circuit             | t <sub>scr</sub>       | C <sub>IN</sub> =470μF to 1000μF                                                         |         | 2.0     |         | μs   |

|                                            |                        | C <sub>IN</sub> =10μF, C <sub>L</sub> =1μF, R <sub>SET</sub> =22kΩ                       | 0.44    | 0.56    | 0.67    |      |

| Current Limit Threshold                    | ILIMIT                 | $C_{\text{IN}}$ =10 $\mu$ F, $C_{\text{L}}$ =1 $\mu$ F, $R_{\text{SET}}$ =12.3 $k\Omega$ | 0.80    | 1.0     | 1.20    | Α    |

|                                            |                        | C <sub>IN</sub> =10μF, C <sub>L</sub> =1μF, R <sub>SET</sub> =4.12kΩ                     | 2.40    | 3.0     | 3.60    |      |

|                                            |                        | C <sub>IN</sub> =10μF, C <sub>L</sub> =1μF, R <sub>SET</sub> =22kΩ                       | 0.33    | 0.42    | 0.51    |      |

| Short-Circuit Current Threshold            | I <sub>SHORT</sub>     | $C_{IN}$ =10 $\mu$ F, $C_L$ =1 $\mu$ F, $R_{SET}$ =12.3 $k\Omega$                        | 0.60    | 0.75    | 0.90    | Α    |

|                                            |                        | C <sub>IN</sub> =10μF, C <sub>L</sub> =1μF, R <sub>SET</sub> =4.12kΩ 1                   |         | 2.25    | 2.70    |      |

| Over-Current FLAG Response Delay Time      | t <sub>D</sub>         | C <sub>IN</sub> =10μF, C <sub>L</sub> =1μF, V <sub>OUT</sub> =0 until<br>FLAG is low     |         | 13      | 20      | ms   |

| FLAG Output Low Voltage                    | V <sub>FLAG_L</sub>    | C <sub>IN</sub> =10µF, I <sub>SINK</sub> =2mA                                            |         |         | 200     | mV   |

| FLAG Output Leakage Current                | I <sub>FLAG_L</sub>    | C <sub>IN</sub> =10µF, V <sub>FLAG</sub> =5.0V                                           |         | 0.1     | 1.0     | μΑ   |

| Discharge Resistor                         | R <sub>Discharge</sub> | C <sub>IN</sub> =10µF, Switch off                                                        |         | 300     | 350     | Ω    |

| Thermal Shutdown Temperature               | T <sub>SD</sub>        | C <sub>IN</sub> =10µF                                                                    |         | 150     |         | °C   |

| Thermal Shutdown Hysteresis                | T <sub>SD_HY</sub>     | C <sub>IN</sub> =10µF                                                                    |         | 20      |         | °C   |

<sup>(1)</sup> Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

<sup>(2)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

#### **8.6 PARAMETER MEASUREMENT INFORMATION**

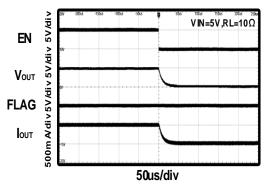

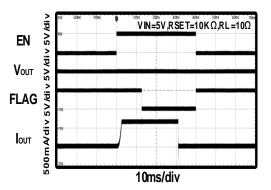

Figure 1. Switch Turn-On and Turn-Off Delay Time

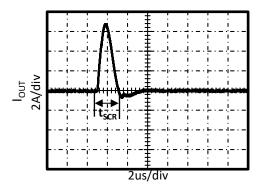

Figure 2. Short-Circuit Response Time

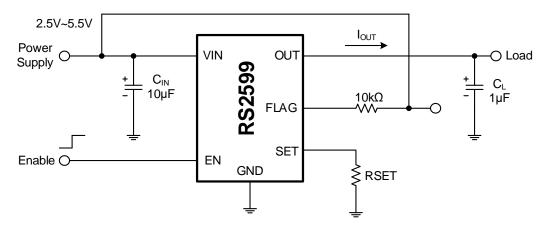

**Figure 3. Typical Application Circuit**

#### 8.7 TYPICAL PERFORMANCE CHARACTERISTICS

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

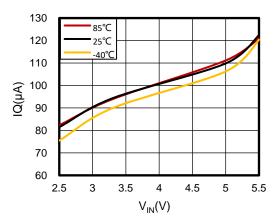

Figure 4. Quiescent Current vs Supply Voltage

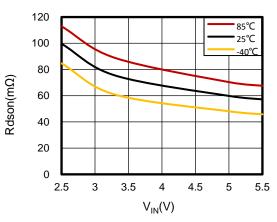

Figure 5. High-side MOSFET On Resistance vs Supply Voltage

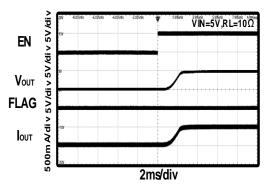

Figure 6. Turn-On Delay Time

Figure 7. Turn-Off Delay Time

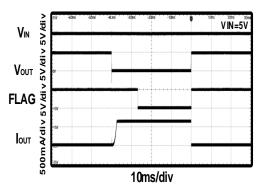

Figure 8. Exit Over Temperature Protection

**Figure 9. Enter Over Temperature Protection**

11 / 17 www.run-ic.com

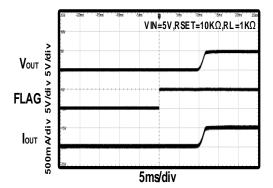

Figure 10. No Load into Short-Circuit

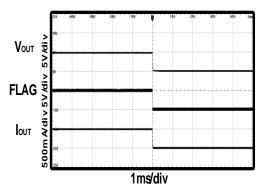

Figure 12. Short-Circuit Response Time

Figure 11. Device Enabled into Short-Circuit

Figure 13. Reverse Input-Output Voltage Protection

#### 9 DETAILED DESCRIPTION

#### 9.1 Input and Output

VIN is the power supply connection to the logic circuitry and the source of the P-channel MOSFET. OUT is the drain of the P-channel MOSFET. In a typical circuit, current flows from VIN to OUT toward the load. The output P-channel MOSFET and driver circuit are also designed to allow the MOSFET drain to be externally forced to a higher voltage than the source  $(V_{OUT} > V_{IN})$  when the switch is disabled.

#### 9.2 Thermal Shutdown

Thermal shutdown is employed to protect device and load from damage because of excessive power dissipation. It shuts off the output MOSFET and asserts the FLAG output, if the die temperature exceeds 150°C until the die temperature drops to 130°C.

#### 9.3 Soft-Start

In order to eliminate the upstream voltage sag caused by the large inrush current during hot-plug events, the soft-start feature effectively isolates power supplies from such highly capacitive loads.

#### 9.4 Under-Voltage Lockout (UVLO)

UVLO prevents the MOSFET switch from turning on until input voltage exceeds 1.9 (Typical). If input voltage drops below 1.8V (Typical), UVLO shuts off the MOSFET switch. Under-voltage detection functions only when the switch is enabled.

#### 9.5 Current Limiting and Short-Circuit Protection

The current limit circuit is designed to limit the output current to protect the upstream power supply. Current limit threshold is programmed with a resistor from SET to ground marked as R<sub>SET</sub>. It can be estimated by the following equation:

$$I_{LIMIT} = \frac{12320}{R_{SET}}$$

,  $I_{SHORT} = 0.75 * \frac{12320}{R_{SET}}$ ,  $R_{SET} \le 24k\Omega$

Under output short-circuit condition; the typical current limit folded back 75%. If the RS2599 keeps at over-current condition for a long time, the junction temperature may exceed 150°C, and over- temperature protection will shut down the output until temperature drops 130°C or limit (short-circuit) condition is removed.

#### 9.6 Reverse-Voltage Protection

The reverse-voltage protection feature turns off the MOSFET switch whenever the output voltage exceeds the input voltage by 50mV (Typical). Its hysteresis voltage is 20mV (Typical). The Output reverse-voltage deglitch time is 13ms (Typical).

#### 9.7 Fault Flag (FLAG)

The signal is an open-drain N-MOSFET output. FLAG is asserted (active low) when an over-current, short-circuit or thermal shutdown condition occurs.

In the case of an over-current condition, FLAG will be asserted only after the response delay time  $(t_D)$  has elapsed. This ensures that FLAG is asserted only upon valid over-current condition and that erroneous error reporting is eliminated.

False over-current condition can occur during hot-plug events when a highly capacitive load is connected and causes a high transient inrush current that exceeds the current limit threshold for up to 1ms. The FLAG response delay time t<sub>D</sub> is 13ms (Typical).

#### 9.8 Power Dissipation

The device's junction temperature depends on several factors such as the load, PCB layout, ambient temperature, and package type. Equations that can be used to calculate power dissipation and junction temperature are found below:

$P_D = R_{DS(ON)} \times I_{OUT}^2$

To relate this to junction temperature, the following equation can be used:

$T_J = P_D \times \theta_{JA} + T_A$

Where:

13 / 17 www.run-ic.com

$T_J$  = junction temperature

$T_A$  = ambient temperature

$\theta_{JA}$  = the thermal resistance of the package

#### 9.9 Supply Filter Capacitor

In order to prevent the input voltage drooping during hot-plug events, connect a ceramic capacitor ( $C_{IN}$ ) from VIN to GND. The  $C_{IN}$  is positioned close to VIN and GND of the device. However, higher capacitor values could reduce the voltage sag on the input further. Furthermore, an output short will cause ringing on the input without the input capacitor. It could destroy the internal circuitry when the input transient exceeds 6.0V which is the absolute maximum supply voltage even for a short duration.

If the upstream supply cable is long or the VIN transient exceeds 6.0V during the V<sub>OUT</sub> short, recommend adding a second filter capacitor (not less than 47µF) at the upstream supply output terminal.

#### 9.10 Output Filter Capacitor

A low-ESR 10uF ceramic capacitor between OUT and GND is strongly recommended to reduce the voltage droop during hot-attachment of downstream peripheral. Higher value output capacitor is better when the output load is heavy. Additionally, bypassing the output with a 0.1uF ceramic capacitor improves the immunity of the device to short-circuit transients.

#### 9.11 PCB Layout Guide

For best performance of the RS2599, the following guidelines must be strictly followed:

- 1. Please place the input capacitors near the VIN pin as close as possible.

- 2. Keep VIN and OUT traces as wide and short as possible.

- 3.Locate RS2599 and output capacitors near the load to reduce parasitic resistance and inductance for excellent load transient performance.

- 4.Input and output capacitors should be placed closed to the IC and connected to ground plane to reduce noise coupling. Place a ground plane under all circuitry to lower both resistance and inductance and improve DC and transient performance

- 5.The traces routing the R<sub>ILIM</sub> resistor to the RS2599 should be as short as possible to reduce parasitic effects on the current limit accuracy.

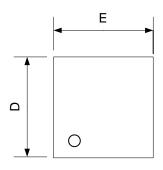

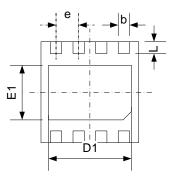

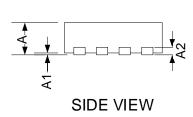

#### 10 PACKAGE OUTLINE DIMENSIONS DFN3x3-8L

**TOP VIEW**

**BOTTOM VIEW**

0.65 0.30 2.86 RECOMMENDED LAND

PATTERN (Unit: mm)

| Cumbal | Dimensions | In Millimeters | Dimension | s In Inches |  |

|--------|------------|----------------|-----------|-------------|--|

| Symbol | Min        | Max            | Min       | Max         |  |

| А      | 0.700      | 0.800          | 0.028     | 0.031       |  |

| A1     | 0.000      | 0.050          | 0.000     | 0.002       |  |

| A2     | 0.2        | 203            | 0.008     |             |  |

| b      | 0.250      | 0.350          | 0.010     | 0.014       |  |

| D      | 2.900      | 3.100          | 0.114     | 0.122       |  |

| D1     | 2.350      | 2.450          | 0.093     | 0.096       |  |

| Е      | 2.900      | 3.100          | 0.114     | 0.122       |  |

| E1     | 1.650      | 1.750          | 0.065     | 0.069       |  |

| е      | 0.650      | ) TYP          | 0.026 TYP |             |  |

| L      | 0.370      | 0.470          | 0.015     | 0.019       |  |

#### NOTE:

- A. All linear dimension is in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

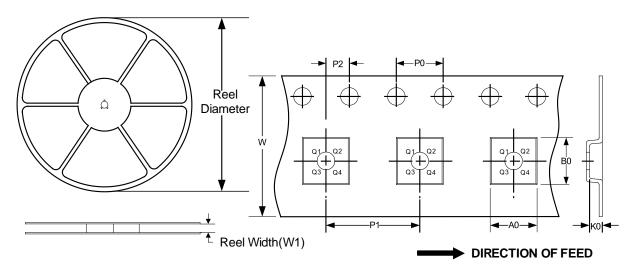

#### 11 TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

#### **TAPE DIMENSION**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package<br>Type | Reel<br>Diameter | Reel<br>Width<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|------------------|-----------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| DFN3×3-8L       | 13"              | 12.4                  | 3.35       | 3.35       | 1.13       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

NOTE:

<sup>1.</sup> All dimensions are nominal.

<sup>2.</sup> Plastic or metal protrusions of 0.15mm maximum per side are not included.

#### IMPORTANT NOTICE AND DISCLAIMER

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.