在紛雜的微處理器系統(tǒng)設計當中,處理器與外圍電路的搭配方式是多種多樣的。但對于處理器來講,它的啟動方式卻是一成不變的,運行過程中嚴格、準確地重復執(zhí)行函數(shù)和指令。因此,啟動電壓,時序等參數(shù)的正確與否成為了衡量一個電子系統(tǒng)魯棒性好壞的標準之一。復位芯片就此應運而生。

復位芯片通常與處理器、穩(wěn)壓器等結合使用。它可以針對電源軌監(jiān)控,以確保系統(tǒng)上電。與此同時,復位芯片也可以檢測故障并與處理器進行通信,保障系統(tǒng)安全運行。本文將以RS706為例,討論帶看門狗的復位芯片在應用設計中的注意事項。

?

RS706概述

?

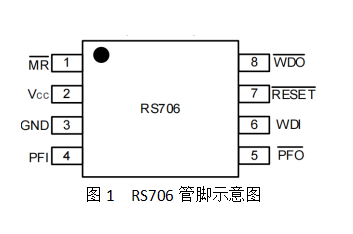

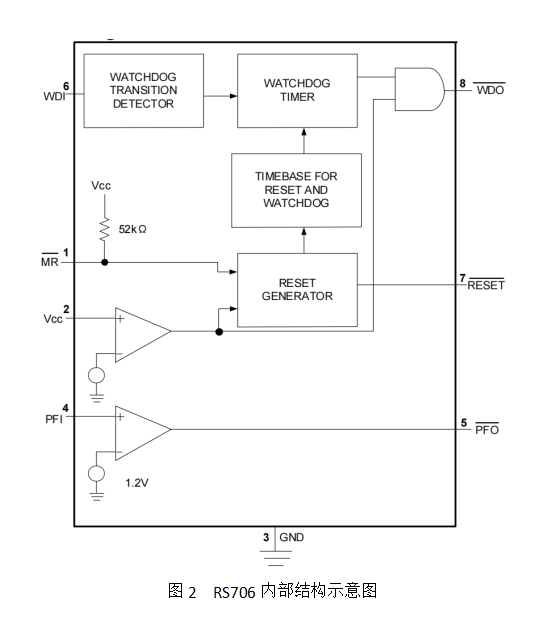

RS706是內部集成電源電壓監(jiān)控,上電復位,看門狗及手動復位四種功能的多功能復位芯片,參數(shù)概括如下:

l 工作電壓范圍:1.0V至5.5V

l? 功耗:40μA(最大值)

l 電源電壓監(jiān)控閾值:2.63V、2.93V、3.08V、4.00V

l 支持手動復位輸入

l 復位脈寬:200ms

l 獨立看門狗定時器:時鐘周期1.6秒(典型值)

l 支持PFI輸入:可作為電源故障或電池低電量功能的監(jiān)測

l 工作溫度范圍:-40℃至+85℃

l 封裝:SOIC-8

?

???????????

?

?

手動復位

?

在特定的持續(xù)時間內(大于TMR:15ns),當手動復位引腳( )的輸入電壓低于手動復位閾值電壓低電平(WDI Input Threshold-Low)時,

)的輸入電壓低于手動復位閾值電壓低電平(WDI Input Threshold-Low)時, 將輸出低電平。只要

將輸出低電平。只要 引腳持續(xù)保持低電平,復位引腳

引腳持續(xù)保持低電平,復位引腳 也將持續(xù)輸出低電平。當

也將持續(xù)輸出低電平。當 持續(xù)高于手動復位閾值電壓高電平(WDI Input Threshold-Low)后,

持續(xù)高于手動復位閾值電壓高電平(WDI Input Threshold-Low)后, 引腳會在1個復位脈寬(TRS)到期后拉高。其中

引腳會在1個復位脈寬(TRS)到期后拉高。其中 引腳內部支持去抖的功能,電氣上可兼容TTL和CMOS邏輯,既可以由外部的邏輯線路驅動也可以由短路到地的按鈕觸發(fā)。

引腳內部支持去抖的功能,電氣上可兼容TTL和CMOS邏輯,既可以由外部的邏輯線路驅動也可以由短路到地的按鈕觸發(fā)。

?

設計注意事項:

設計注意事項:

?

l?RS706的 復位脈寬(TRS)在100至350ms之間,設計中需要結合該時間的最小值核對處理器對復位信號脈寬的要求。

復位脈寬(TRS)在100至350ms之間,設計中需要結合該時間的最小值核對處理器對復位信號脈寬的要求。

l?VCC電壓上升超過復位閾值電壓或者 引腳拉高后,

引腳拉高后, 引腳仍然會保持一個復位周期的時間。

引腳仍然會保持一個復位周期的時間。

l?需注意 的復位電平是否與處理器的復位電平邏輯一致。

的復位電平是否與處理器的復位電平邏輯一致。

l?假如復位信號走線過長,很容易引入干擾,從而導致復位信號驅動能力不足,這種情況可以加入RS1G125驅動器來解決。

電源電壓監(jiān)控

?

VCC輸入支持精準的電壓監(jiān)控,可以監(jiān)控復位芯片的供電電壓是否有突變。

?

電源電壓監(jiān)控設計注意事項:

?

l選型和應用中需要評估VCC的復位閾值電壓是否滿足設計需求。例如RS706-2.93YK,2.93V為其電源監(jiān)控閾值的典型值,實際中對于不同芯片來看,該值是在2.86V至3.0V之間。設計時需要特別關注該最大值是否可滿足需求。

?

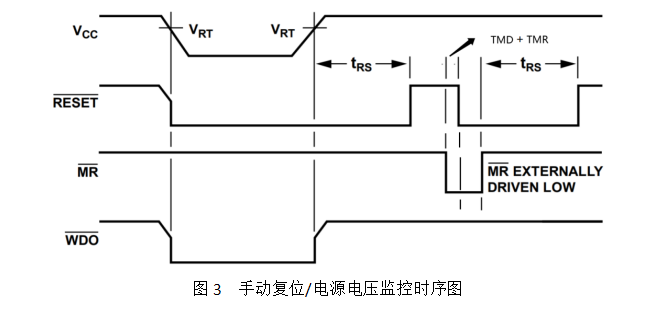

手動復位和電源電壓監(jiān)控的時序圖如下:

?

?

當復位芯片的電源下電(VCC下降至VRT)或者上電(VCC上升至VRT)時, 均會發(fā)出一個以脈寬長度為TRS的低電平信號。VCC上電穩(wěn)定后,需要至少

均會發(fā)出一個以脈寬長度為TRS的低電平信號。VCC上電穩(wěn)定后,需要至少 被拉低TMR(15ns TYP)的時間,才可正常識別出手動復位信號,然后經(jīng)過TMD(23ns ?TYP)的時間后輸出脈寬長度為TRS的低電平信。

被拉低TMR(15ns TYP)的時間,才可正常識別出手動復位信號,然后經(jīng)過TMD(23ns ?TYP)的時間后輸出脈寬長度為TRS的低電平信。

?

電源故障輸入

?

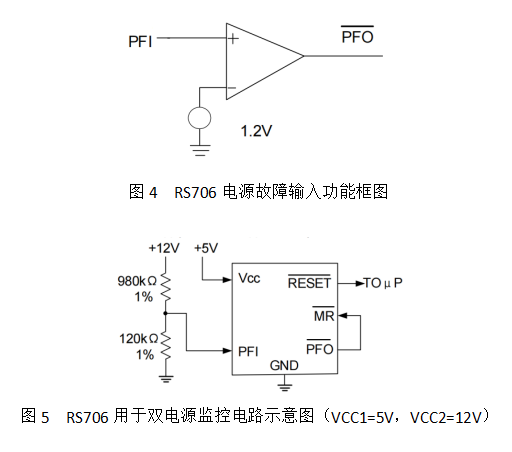

RS706的電源故障輸入功能,是一個參考電壓為1.2V的電壓比較電路,因此對于RS706來說,它除了可以監(jiān)控給自身供電的VCC1電壓之外,還可以監(jiān)控另一路輸入電源VCC2的故障與否。若電源故障輸入(PFI)引腳低于電源故障電壓閾值(PFI Input Threshold),則電源故障輸出( )降低。此外,PFI引腳還可連接到

)降低。此外,PFI引腳還可連接到 引腳,以用于監(jiān)控器/復位IC的低電平復位信號輸出。

引腳,以用于監(jiān)控器/復位IC的低電平復位信號輸出。

?

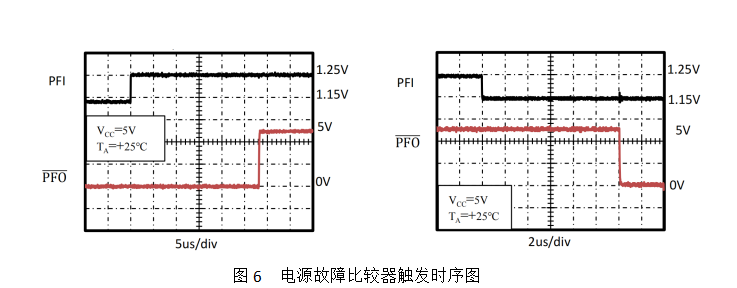

當PFI輸入高于或低于內部比較器的參考電壓(PFI Input Threshold)的時候,經(jīng)過一定的延時時間后,會觸發(fā) 輸出對應高電平或低電平。VCC=5V的時候,時序圖如下:

輸出對應高電平或低電平。VCC=5V的時候,時序圖如下:

?

?

PFI功能設計注意事項:

?

l?在設計中若不使用該功能,可將PFI接入VCC或者GND中,以防止復位芯片輸出不穩(wěn)定。

?

看門狗定時器

?

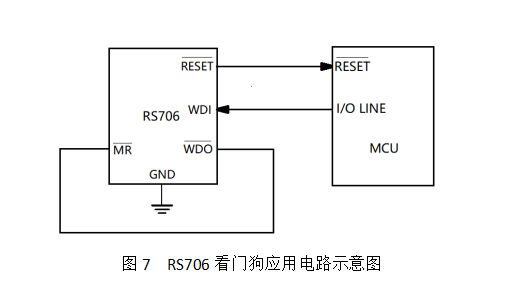

RS706會一直監(jiān)控看門狗輸入( )引腳上的信號。若RS706未在看門狗的定時器周期內檢測到喂狗信號,則觸發(fā)

)引腳上的信號。若RS706未在看門狗的定時器周期內檢測到喂狗信號,則觸發(fā)![]() 輸出。一種常見的應用電路是將

輸出。一種常見的應用電路是將![]() 直連到

直連到 引腳上,即可通過看門狗定時器觸發(fā)

引腳上,即可通過看門狗定時器觸發(fā) 輸出。

輸出。

?

?

?

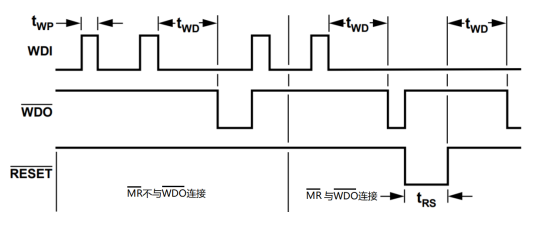

當![]() 與

與 引腳未連接時,若看門狗輸入WDI在看門狗的定時器周期(TWD)內沒有收到脈寬信號至少在TWP(16ns ?min)的喂狗信號,則觸發(fā)

引腳未連接時,若看門狗輸入WDI在看門狗的定時器周期(TWD)內沒有收到脈寬信號至少在TWP(16ns ?min)的喂狗信號,則觸發(fā)![]() 的低電平輸出,該

的低電平輸出,該![]() 的低電平保持至下次WDI脈沖信號到來。

的低電平保持至下次WDI脈沖信號到來。

當 與

與 引腳連接時,若看門狗輸入WDI在看門狗的定時器周期(TWD)內沒有收到脈寬信號至少在TWP(16ns ?min)的喂狗信號,則觸發(fā)

引腳連接時,若看門狗輸入WDI在看門狗的定時器周期(TWD)內沒有收到脈寬信號至少在TWP(16ns ?min)的喂狗信號,則觸發(fā)![]() 的低電平輸出。該

的低電平輸出。該![]() 低電平的持續(xù)時間很短。這是因為當看門狗超時后,

低電平的持續(xù)時間很短。這是因為當看門狗超時后,![]() 輸出低電平至

輸出低電平至 時,會立即使

時,會立即使 引腳輸出低電平,而

引腳輸出低電平,而 引腳的低電平會清零看門狗定時器標志位,

引腳的低電平會清零看門狗定時器標志位, 的優(yōu)先級要高于看門狗。

的優(yōu)先級要高于看門狗。

兩種連接狀態(tài)下的波形圖如下:

?

???????????????????????? 圖8 ?RS706看門狗信號時序圖

?

看門狗設計注意事項:

?

l?喂狗的時機:WDI輸入保持高電平或者低電平超出定時器的周期TWD,則內部看門狗超時,![]() 輸出低電平,注意1.6s給出的是典型值,實際上RS706的該時間范圍是在1.0s至2.9s之間

輸出低電平,注意1.6s給出的是典型值,實際上RS706的該時間范圍是在1.0s至2.9s之間

l?如何喂狗:在看門狗的溢出周期之內,WDI引腳電平發(fā)生變化即可認為成功實現(xiàn)了喂狗操作,計數(shù)器將清零需要注意TWP這個參數(shù),對于RS706來講,TWP要求至少在16ns以上。

l?WDI走線不宜過長并遠離干擾源,以防止喂狗信號受干擾。

l?看門狗的禁用:可以將WDI引腳浮空或者連接到高阻抗狀態(tài)的三態(tài)緩沖器上,從而禁用看門狗功能。

?

其他注意事項:

l?在復位芯片的設計中需要注意管腳的結構屬性,包括開漏和推挽兩種,在實際設計中需要根據(jù)處理器復位管腳的屬性來選擇。

2022-06-15

2022-06-15